PowerLattice Secures $25 Million Series A to Cut AI Chip Power Consumption by Over 50%

Vancouver, WA – PowerLattice, a company specializing in power delivery for artificial intelligence (AI) accelerators, has emerged from stealth mode, announcing a $25 million Series A funding round. This investment, jointly led by Playground Global and Celesta Capital, brings the company's total funding to $31 million. The capital will be used to further develop its groundbreaking power delivery chiplet, designed to significantly reduce compute power needs for next-generation AI.

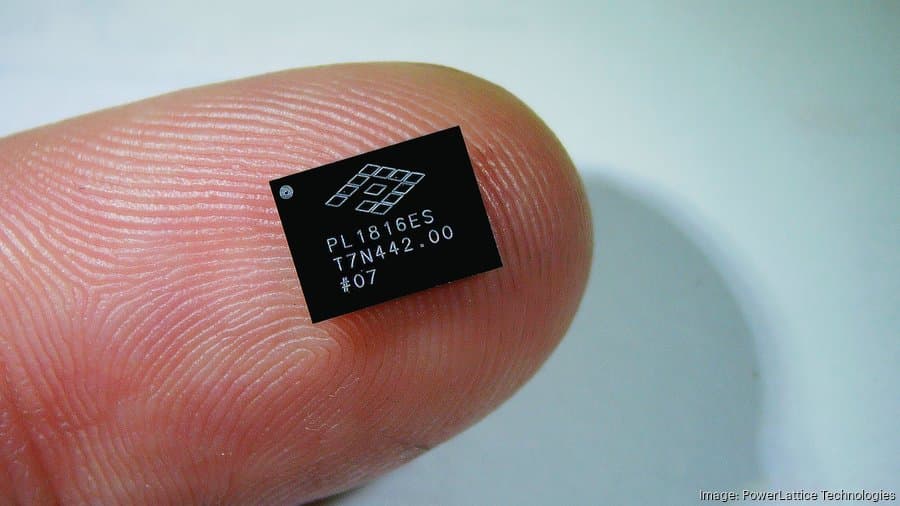

The core of PowerLattice's innovation is a power delivery chiplet that integrates power directly into the processor package, aiming to cut total compute power requirements by more than 50% and effectively double performance. Dr. Peng Zou, Co-Founder, CEO, and President of PowerLattice, emphasized the criticality of this development, stating, > "Power is the defining challenge for AI’s future. Data centers are already starting to hit a power wall and the problem is only going to get worse if we don’t rethink how chips are powered."

The technology addresses a growing concern in the AI industry, where accelerators and GPUs are pushing past 2 kilowatts per chip, straining data center infrastructure. Conventional power delivery methods lead to energy waste and performance limitations due to long, resistive electrical current paths. PowerLattice's solution brings power closer to the computation, utilizing miniaturized on-die magnetic inductors, advanced voltage control circuits, and a programmable software layer.

Pat Gelsinger, General Partner at Playground Global and former Intel CEO, highlighted the significance of PowerLattice's approach. He remarked, > "AI is not constrained by capital, it’s constrained by power. PowerLattice represents a dramatic breakthrough in the efficiency and scale of power delivery." The company's chiplet is designed for seamless integration into existing system-on-a-chip (SOC) designs, reducing overall processor footprint and shortening power paths.

Founded by semiconductor veterans Peng Zou, Gang Ren, and Sujith Dermal, with backgrounds from Qualcomm, NUVIA, and Intel, PowerLattice is already providing engineering samples for 1 KW+ GPUs, CPUs, and accelerators. The company's technology promises to unlock chip performance by reducing power-related throttling and increasing compute utilization, thereby enabling more AI computation per rack and delivering AI-grade reliability.